# **MIPS<sup>®</sup> SDE 5.03 Programmers' Guide**

Document Number: MD00310 Revision 1.67 January 7, 2004

MIPS Technologies, Inc 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 1995-2004 MIPS Technologies, Inc. All rights reserved.

Copyright © 1995-2004 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS16, QuickMIPS, R3000 and R5000 are among the registered trademarks of MIPS Technologies, Inc. in the United States and other countries, and MIPS16e, MIPS32, MIPS64, MIPS-3D, MIPS-Based, MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS RISC Certified Power logo, MIPSsim, MIPS Technologies logo, R4000, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 20Kc, 24K, 24Kf, 24Kc, 25Kf, ASMACRO, ATLAS, At the Core of the User Experience., BusBridge, CorExtend, CoreFPGA, CoreLV, EC, FastMIPS, JALGO, MALTA, MDMX, MGB, PDtrace, The Pipeline, Pro Series, SEAD, SEAD-2, SmartMIPS, SOC-it and YAMON are among the trademarks of MIPS Technologies, Inc.

All other trademarks referred to herein are the property of their respective owners.

Template: B1.10, Built with tags: 2B MIPS32/MIPS64 SUM

## **Open Source Copyright Notices**

Many of the utilities contained in this package are derived from Free Software Foundation code, which require this notice:

This program is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 1, or (at your option) any later version.

This program is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with this program; if not, write to the Free Software Foundation, 675 Mass Ave, Cambridge, MA 02139, USA.

See also http://www.fsf.org/licenses/licenses.html.

The Windows version of MIPS<sup>®</sup> SDE is built using the *Cygwin* programming environment, produced by RedHat/Cygnus at http://www.cygwin.com, and is distributed under the terms of the GNU General Public License and Cygwin API license, see http://cygwin.com/licensing.html.

Some of the target libraries contain modules which require this acknowledgement:

This product includes software developed by the University of California, Berkeley and its contributors.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Ltd. X/Open is a trademark of X/Open Company Ltd. POSIX is a registered trademark of the Institute of Electrical and Electronics Engineers, Inc.

For more details on how these copyrights affect the code that you develop using MIPS<sup>®</sup> SDE, see Appendix A "Copyrights".

## Table of Contents

| Open Source Copyright Notices                     | 0  |

|---------------------------------------------------|----|

| 1. Introduction                                   |    |

| What's in MIPS <sup>®</sup> SDE                   |    |

| The MIPS <sup>®</sup> SDE <i>lite</i> subset      | 11 |

| Getting working fast                              |    |

| Other reading                                     |    |

| Other toolchain documentation                     |    |

| 2. SDE on UNIX and Windows                        |    |

| 2.1. SDE on Windows and "Cygwin"                  |    |

| 2.1.1. File pathnames in Windows with Cygwin      |    |

| 2.1.2. Text and binary files in Cygwin            | 14 |

| 2.2. Environment variables                        | 15 |

| 3. Installation                                   |    |

| 3.1. Minimum System Requirements                  |    |

| 3.2. Environment Variable Setup                   |    |

| 3.3. Installation                                 |    |

| What's in the internet download?                  |    |

| Where should you install your package?            |    |

| Install MIPSsim <sup>™</sup> simulator and probes |    |

| Remove old SDE                                    |    |

| Windows: Install Cygwin                           |    |

| Install SDE                                       | 19 |

| 3.4. Multi-User Installation                      |    |

| 4. Quick Start                                    |    |

| 5. Overview                                       |    |

| Command lines, make and makefiles                 |    |

| Program Editor                                    |    |

| Make                                              |    |

| C Compiler                                        |    |

| C++ Compiler                                      |    |

| MIPS <sup>®</sup> Assembler                       |    |

| Binary Utilities                                  |    |

| ECOFF compatibility                               |    |

| Download Tools                                    |    |

| Libraries                                         |    |

| Header Files                                      |    |

| Embedded System Kit                               |    |

| Micromon                                          |    |

| Example Programs                                  |    |

| Source Level Debugger                             |    |

| GNU MIPS <sup>®</sup> CPU Simulator               |    |

| MIPSsim <sup>™</sup> Simulator                    |    |

| Online Documentation                              |    |

| 6. Online Documentation                           |    |

| Browsable HTML pages                              |    |

| Printable manuals                                 |    |

| 7. Target Specific Libraries                      |    |

| 7.1. Building for ISA and CPU Variants            |    |

|                                                   |    |

| 8. Example Programs                                                          |  |

|------------------------------------------------------------------------------|--|

| 8.1. Individual Examples                                                     |  |

| 8.1.1. Hello World!                                                          |  |

| 8.1.2. TLB Exception Handling (tlbxcpt)                                      |  |

| 8.1.3. Command Line Monitor (minimon)                                        |  |

| 8.1.4. Floating Point Test (paranoia)                                        |  |

| 8.1.5. Dhrystone Benchmark                                                   |  |

| 8.1.6. Whetstone Benchmark                                                   |  |

| 8.1.7. Linpack Benchmark                                                     |  |

| 8.1.8. C++ Demo                                                              |  |

| 8.1.9. Kit Test                                                              |  |

| 8.1.10. Flash Memory Test                                                    |  |

| 8.1.11. PCI Bus Demo                                                         |  |

| 8.1.12. Decompressing Boot Loader                                            |  |

| 8.2. Example Makefiles                                                       |  |

| 9. Porting an ANSI C Program                                                 |  |

| Common problems when converting to MIPS <sup>®</sup> architecture            |  |

| 10. Standard Libraries                                                       |  |

| 10.1. ANSI C Library                                                         |  |

| Input and Output: <stdio.h></stdio.h>                                        |  |

| Character Class Tests: <ctype.h></ctype.h>                                   |  |

| String Functions: <string.h></string.h>                                      |  |

| Mathematical Functions: <math.h></math.h>                                    |  |

| Utility Functions: <stdlib.h></stdlib.h>                                     |  |

| Diagnostics: <assert.h></assert.h>                                           |  |

| Variable Argument Lists: <stdarg.h></stdarg.h>                               |  |

| Non-local Jumps: <setjmp.h></setjmp.h>                                       |  |

| Signals: <signal.h></signal.h>                                               |  |

| Date and Time Functions: <time.h></time.h>                                   |  |

| Implementation-defined Limits: <li>limits.h&gt; and <float.h></float.h></li> |  |

| 10.1.1. ISO C99 library support                                              |  |

| 10.1.2. Minimal C library                                                    |  |

| 10.2. IEEE-754 Floating Point Emulation Library                              |  |

| 10.2. Multilibs                                                              |  |

| 10.4. Source Code                                                            |  |

|                                                                              |  |

| 11. Compiler Options                                                         |  |

| 11.1. Architectural Flags                                                    |  |

| 11.1.1. Endianness Flags                                                     |  |

| 11.1.2. Instruction Set Flags                                                |  |

| 11.1.3. CPU Flags                                                            |  |

| 11.2. Optimisation Options                                                   |  |

| 11.2.1. Optimising for Speed                                                 |  |

| 11.2.2. Optimising for Space                                                 |  |

| 11.3. GP-relative Addressing                                                 |  |

| 11.4. Unaligned Data                                                         |  |

| 11.5. Floating Point Support                                                 |  |

| 11.6. 64-bit Support                                                         |  |

| 32/64-bit compatibility                                                      |  |

| 64-bit calling conventions                                                   |  |

| 64-bit addressing – not supported in C                                       |  |

| Optimisation warning                                                         |  |

| 11.6.1. Assembler Enhancements                                               |  |

| 11.7. MIPS16 <sup>TM</sup> and MIPS16e <sup>TM</sup> ASE support             |  |

| Global Variables and MIPS16 <sup>™</sup> code                                |  |

| Global Register Variables                                                    |                                        |

|------------------------------------------------------------------------------|----------------------------------------|

| Allocating 32-bit Registers (-muse-all-regs)                                 |                                        |

| Divide by Zero Checks (-mcheck-zero-division)                                |                                        |

| Execute-only MIPS16 <sup>™</sup> Code                                        |                                        |

| Generating MIPS16 <sup>™</sup> code                                          |                                        |

| Main differences between MIPS16 <sup>TM</sup> and MIPS16e <sup>TM</sup> code |                                        |

| 11.8. Unsupported Compiler Options                                           |                                        |

| 12. Insight Graphical Debugger                                               |                                        |

| 13. Debugging with GDB                                                       |                                        |

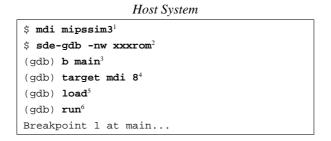

| 13.1. MDI Debugging                                                          |                                        |

| 13.1.1. MDI Debugging with the MIPSsim <sup>™</sup> Simulator                |                                        |

| 13.1.2. MDI Debugging with an EJTAG Probe                                    |                                        |

| 13.1.3. MDI Debugging Tips                                                   |                                        |

| 13.2. Debugging with the GNU Simulator                                       |                                        |

| 13.3. Debugging via a Serial Port                                            |                                        |

| GDB serial ports                                                             |                                        |

| GDB serial ports                                                             |                                        |

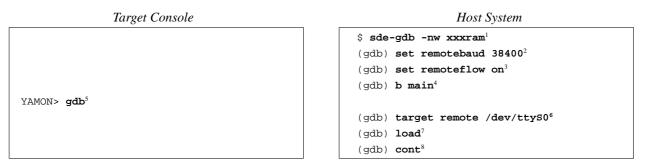

| 13.3.1. Serial Debugging with the YAMON <sup>™</sup> Monitor                 |                                        |

| 13.3.2. Serial Debugging with SDE Debug Stub                                 |                                        |

| 13.3.3. Serial Comms Fault Finding                                           |                                        |

| 13.4. Debugging C++                                                          |                                        |

| 13.5. GDB Changes for Windows                                                |                                        |

|                                                                              |                                        |

| 14. Profiling with GPROF and GCOV                                            |                                        |

| 14.1. Compiler Options for Profiling                                         |                                        |

| 14.1.1. Statistical (PC-sampling)                                            |                                        |

| 14.1.2. Function Call Graph                                                  |                                        |

| 14.1.3. PC Counting                                                          |                                        |

| 14.1.4. Line Granularity                                                     |                                        |

| 14.1.5. Arc Profiling                                                        |                                        |

| 14.1.6. Code Coverage                                                        |                                        |

| 14.1.7. Example Makefile PROFILE Option                                      |                                        |

| 14.2. Profiling with the MIPSsim <sup>™</sup> Simulator                      |                                        |

| 14.2.1. Instruction counting                                                 |                                        |

| 14.2.2. Cycle counting                                                       |                                        |

| 14.2.3. Omitting the Call Graph                                              |                                        |

| 14.2.4. Line Granularity                                                     |                                        |

| 14.2.5. Interactive Cycle Counting                                           |                                        |

| 14.3. Profiling with an EJTAG Probe                                          |                                        |

| 14.4. Profiling with the YAMON <sup>™</sup> Monitor                          |                                        |

| 14.5. Profiling with the GNU Simulator                                       |                                        |

| 14.6. Profile-directed Optimisation                                          |                                        |

| 14.7. Code Coverage Report                                                   |                                        |

| 15. Linker Scripts and Object Files                                          |                                        |

| 15.1. Linker Scripts                                                         |                                        |

| 15.2. ELF Object File Format                                                 |                                        |

| 15.3. ECOFF Object File Format                                               | 80                                     |

| 16. Using Extra Sections                                                     |                                        |

| 16.1. Assembler Sections                                                     |                                        |

| 16.2. C/C++ Sections                                                         |                                        |

| 16.3. Linking Extra Sections                                                 |                                        |

| 16.4. Controlling Garbage Collection                                         |                                        |

| 16.5. Calling Remote Functions                                               |                                        |

| 17. Manual Downloading                                                       |                                        |

| 1 / · · · · · · · · · · · · · · · · · ·                                      | ······································ |

| 17.1. Evaluation Board Download                                    |    |

|--------------------------------------------------------------------|----|

| 17.2. PROM Programmer Download                                     |    |

| 17.3. Other Techniques                                             |    |

| 18. MIPS <sup>®</sup> Intrinsics                                   |    |

| 18.1. Byte Swap Intrinsics                                         |    |

| 18.2. MIPS32 <sup>™</sup> Intrinsics                               |    |

| 18.3. MIPS32 <sup>™</sup> Release 2 Intrinsics                     |    |

| 18.4. MIPS64 <sup>™</sup> Release 2 Intrinsics                     |    |

| 18.5. CorExtend <sup>™</sup> (UDI) Intrinsics                      |    |

| 18.6. COP2 Intrinsics                                              |    |

| 18.7. SmartMIPS <sup>™</sup> Intrinsics                            |    |

| 18.8. Atomic RMW Intrinsics                                        |    |

| 18.9. Prefetch Intrinsics                                          |    |

| 19. SDE Run-time I/O System                                        | 93 |

| 19.1. POSIX API Environment                                        |    |

| 19.1.1. Remote File I/O                                            |    |

| 19.1.2. Terminal I/O (/dev/tty)                                    |    |

| 19.1.2. Flash Memory Device (/dev/flash)                           |    |

| 19.1.4. Alpha Display (/dev/panel)                                 |    |

| 19.1.5. Signal Handling                                            |    |

| 19.1.6. Elapsed Time Measurement                                   |    |

| 19.1.7. Interval Timing                                            |    |

| 19.2. PCI Bus Support                                              |    |

| 20. CPU Management                                                 |    |

| 20. CPO Management                                                 |    |

| 20.1. CPO Initialisation                                           |    |

| 20.2.1. C-level Exceptions                                         |    |

| 20.2.2. RTOS Context Switch                                        |    |

| 20.2.2. Clevel Interrupts                                          |    |

| 20.2. C-level interrupis                                           |    |

| 20.4. TLB Maintenance                                              |    |

| 20.5. Hardware Watchpoints                                         |    |

| 20.6. System Coprocessor (CP0) Intrinsics                          |    |

| Common CP0 Registers                                               |    |

| MIPS32 <sup>TM</sup> /MIPS64 <sup>TM</sup> CP0 Registers           |    |

| MIPS32 <sup>TM</sup> /MIPS64 <sup>TM</sup> Release 2 CP0 Registers |    |

| MIPS32 <sup>TM</sup> /MIPS64 <sup>TM</sup> Release 2 Shadow Sets   |    |

| 20.7. Miscellaneous                                                |    |

| 20.8. Floating Point Coprocessor (CP1)                             |    |

| Coprocessor 1 Emulation                                            |    |

| -                                                                  |    |

| 21. Embedded System Kit Source                                     |    |

| 21.1. POSIX System Interface                                       |    |

| 21.1.1. Run-time Initialisation                                    |    |

| 21.1.2. Run-time Termination                                       |    |

| 21.2. Target-specific Code                                         |    |

| 21.2.1. PCI Bus Configuration                                      |    |

| 21.3. Monitor-specific Glue                                        |    |

| 21.4.1 CPU Management                                              |    |

| 21.4.1. CPU Reset Handling                                         |    |

| 21.4.2. Exception Handlers                                         |    |

| 21.4.3. Remote Debug Stub                                          |    |

| 22. Retargetting the Toolkit                                       |    |

| 22.1. Common Device Files                                          |    |

| 23. Known Problems                                   |     |

|------------------------------------------------------|-----|

| Download Tools                                       |     |

| GNU MIPS <sup>®</sup> Simulator                      |     |

| GDB MDI Hardware Watchpoints                         |     |

| GDB and MIPSsim <sup>™</sup> 4.x                     |     |

| 24. Getting Support                                  |     |

| Upgrading                                            |     |

| Internet data at MIPS Technologies                   |     |

| Related Services                                     |     |

| 25. References                                       |     |

| Appendix A: Copyrights                               |     |

| Appendix B: MIPS <sup>®</sup> Freedom-to-Use License |     |

| Appendix C: Release History                          |     |

| Release 5.03.06 Update                               |     |

| Release 5.03.05 Update                               |     |

| Release 5.03.04 Update                               |     |

| Release 5.03.03 Update                               |     |

| Release 5.03.02 Update                               |     |

| Release 5.02.02 Update                               |     |

| Release 5.02 Update                                  |     |

| Release 5.01 Update                                  |     |

| Release 5.0 Update                                   |     |

| Appendix D: Key facts                                |     |

| File pathnames and tree of installation files        |     |

| Environment variables                                |     |

| Non-standard installations                           |     |

| Makefiles                                            |     |

| Makefiles and their hierarchy                        |     |

| Appendix E: Unsupported Targets                      |     |

| Appendix F: Document revision history                | 140 |

## Figures

| Figure 5-1 Programs, libraries and source files in SDE |  |

|--------------------------------------------------------|--|

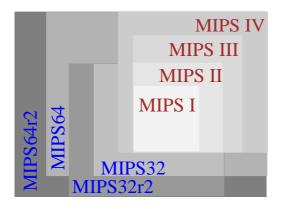

| Figure 11-1 Relationship of MIPS <sup>®</sup> ISAs     |  |

## Tables

| Table 3-1: Installable tar files                                 | 20  |

|------------------------------------------------------------------|-----|

| Table 7-1: Supported target boards and simulators                |     |

| Table 8-1: Example Makefile output files                         |     |

| Table 8-2: User-changeable "Make" variables for program building |     |

| Table 11-1: List of –mcpu names                                  |     |

| Table 13-1: Host O/S serial port devices                         |     |

| Table 15-1: Standard ELF section names                           | 79  |

| Table 16-1: Section attribute flags                              | 81  |

| Table 19-1: Flash memory partition types                         | 94  |

| Table 19-2: POSIX signal list                                    | 99  |

| Table 20-1: Interrupt priorities                                 | 106 |

| Table 20-2: Hardware watchpoint attributes                       | 109 |

| Table 20-3: Watchpoint return codes                              | 109 |

| Table 20-4: CP0 register access intrinsics                       | 111 |

| Table 21-1: Supported PROM monitors                              |     |

| Table 22-1: Board-specific files                                 |     |

#### Chapter 1.

## Introduction

This is a programmers' guide for MIPS Technologies' Software Development Environment for MIPS-based<sup>™</sup> products (henceforth just called "SDE" in this manual).

SDE is a software engineer's cross-development system for MIPS architecture processors, intended for staticallylinked embedded applications running on "bare metal" CPUs or light-weight operating systems<sup>1</sup>. It is a component of the MIPS<sup>®</sup> Software Toolkit (henceforth "MTK"), which includes not only SDE, but other tools and libraries intended to accelerate the development of high quality, high performance applications running on MIPS Technologies' cores. Another key component of MTK is the powerful MIPSsim<sup>™</sup> simulator. Expect to see additional components being added to MTK in future releases.

This manual describes the supported version of MIPS<sup>®</sup> SDE included in the MIPS<sup>®</sup> Software Toolkit, as well as a freely downloadable, but unsupported subset called MIPS<sup>®</sup> SDE *lite*.

SDE provides much more than just prebuilt GNU binaries; it has everything that you need to build and debug downloadable and, for some targets, standalone rommable code (including MIPS-specific low-level CPU initialisation and management). It is hosted on Windows NT, 2000 and XP, Linux/x86, Sun Solaris, and HP HP–UX.

### What's in MIPS<sup>®</sup> SDE

SDE is built around GNU tools tuned, enhanced and packaged by MIPS Technologies together with a set of C and C++ libraries, and a workable single-tasking run-time system. It is maintained independently, by which we mean we will never tell a supported customer that they need to wait while someone else fixes something – and, implicitly, that we maintain our own independently tested codebase.

The SDE run-time system includes convenient C interfaces to pretty much every strange thing you'll have to program on a MIPS-based processor. At a higher level it conforms closely to POSIX standards – so if you need to port your software to or from other operating systems or CPUs, then there's a road open.

SDE is command-line based, and if your background is with PC "integrated development environments" that may come as a culture shock. But stay with us; there's certainly a lot to learn about tools of this kind, but most of it can be learned while you are doing useful work. If you're not quite up to speed on command-lines, read Chapter 5 "Overview". Then read the rest of this page for some useful jumping-off points into the rest of this manual.

The SDE toolkit is structured around a number of example programs, each of which can be built out of the box for the simulators we include, or for any of the supported evaluation boards. You will be going with the flow if you try one of the examples first, and pick one of the examples as a template for any software you want to port to the MIPS architecture.

### The MIPS<sup>®</sup> SDE *lite* subset

The GNU tools themselves are freely redistributable software, and MIPS Technologies provides a free-to-download subset of SDE, called SDE *lite*. It has the same features as the full version, but the proprietary run-time software is provided only as precompiled libraries, not as reusable source code. More important: the free version does not come with support. For more information about your rights and obligations regarding the use of derived binaries see Appendix B "MIPS<sup>®</sup> Freedom-to-Use License". But if you've used the free version, like what you've seen so far, and want to upgrade to the full, supported version, then see Chapter 24 "Getting Support". From now on we'll normally just say "SDE" when we mean either the full SDE, or SDE *lite*.

<sup>&</sup>lt;sup>1</sup> We also have a version of our toolchain configured as a Linux/MIPS native compiler, generating MIPS/abi PIC code, but this manual does not describe that.

## Getting working fast

To get started right away, first follow the installation instructions from many Chapter 3 "Installation", and then proceed straight to Chapter 4 "Quick Start", which shows how to run the simplest possible program on the easiest possible MIPS-based target – a software simulator supplied with SDE.

If your priority is to run some particular programs – perhaps benchmarks – on one of the evaluation boards or simulators ("targets") supported by SDE, then the next thing to do is to build the support library for your target, as described in Chapter 7 "Target Specific Libraries". You can then try running one or both of the benchmark examples (*dhrystone* and *whetstone*) provided with SDE: see Section 8.1.5 "Dhrystone Benchmark".

If you have any problems compiling your own benchmark – and certainly before you tell anyone else the results – you should read Chapter 9 "Porting an ANSI C Program", which warns of potential portability problems. If that's not enough, then Chapter 13 "Debugging with GDB" shows you how to connect the source-level debugger to your target and find out what's going wrong. And read Section 11.2 "Optimisation Options" and Chapter 14 "Profiling with GPROF and GCOV" to see how you can improve your results.

If you are developing or porting a more complex program that needs low-level access to the hardware, then SDE also provides some viable and robust run-time components. Read Chapter 19 "SDE Run-time I/O System" for a description of the programmer's interface to the CPU management functions.

If you need to study or modify the run-time system and CPU management source code, then refer to Chapter 21 "Embedded System Kit Source", which is a guide to its structure. If you want to run programs on a board or other target which is not already supported by SDE, then you will have to write some new board-specific code. Chapter 22 "Retargetting the Toolkit" tells you how you can save effort by writing your board support code the SDE way. In either case, you'll need more source code than is provided in the SDE *lite* subset – you'll need to have a supported version.

Throughout most of this manual we'll show file locations relative to the directory where you install SDE by starting them off with three dots (an ellipsis) and using UNIX-style forward slashes, like this: .../sde/examples. See Section 2.1.1 "File pathnames in Windows with Cygwin" and Section 3.3 "Installation" for more details.

## **Other reading**

In Chapter 25 "References" at the end of the manual you'll find details of other books we've found helpful. But two in particular are worth getting at this stage:

- To understand what makes the MIPS architecture different, get used to the MIPS buzzwords, and feel some comfort with MIPS programming at the assembly language level you should read *See MIPS Run* [Sweet99]<sup>2</sup>

- If you're going to use SDE's libraries and run-time system it's worth getting hold of the *POSIX Programmer's Guide* [Lewine91].

In fact, this may be a good time to take a quick look at Chapter 25 "References" and run up a bill at your local computing bookshop, or Amazon.

## Other toolchain documentation

The individual GNU tools which make up so much of SDE have individual generic manuals: [Binutils], [Cpp], [Gcc], [Gdb], [Gprof], [Ld], [Make], [Stabs]. Where appropriate the versions we supply have been updated to cover MIPS- or SDE-specific features.

The manuals are extensive, very detailed and cover many different CPU types; many are very well-written and are an excellent, but not fast, read. We don't include printed versions with our software package, but you will have HTML versions you can read on-line with your web browser as described in Chapter 6 "Online Documentation", and PDF/Acrobat versions you can print out for yourself.

Other components of the MIPS® Software Toolkit package come with their own detailed manuals.

<sup>&</sup>lt;sup>2</sup> The square brackets tell you that this is a reference to another publication, listed in Chapter 25 "References".

#### Chapter 2.

## **SDE on UNIX and Windows**

While SDE runs well on Windows systems, its origins were on UNIX. SDE is ported to Windows using the "Cygwin" system, as described in this chapter, and Cygwin supports both Windows pathnames (with back-slashes) and UNIX-style file pathnames with forward-slashes. As supplied all SDE's build examples are written with UNIX-style pathnames; so the following sections explain the important issues for Windows users.

## 2.1. SDE on Windows and "Cygwin"

SDE tools are real 32-bit Windows applications, but apart from the debugger they're command-line programs most easily launched from a console window; that might be from inside the debugger, a programmer's editor, or the UNIX-like Cygwin command-line "shell" window.

If this is new to you don't panic yet: you rarely need to type a command more complicated than "sde-make something", unless you get to like command lines. Windows users are likely to wrap the command line tools up using a commercial programmer's editor, browser or "IDE" product. Most of the popular compiler-independent front-ends are readily configured around GNU tools.

To keep the sources as similar as possible, the version for Windows is built using the "Cygwin" DLL<sup>3</sup>. Cygwin offers a POSIX<sup>4</sup>-compatible API for Windows, allowing us to build UNIX and Win32 versions of software from the same sources, with relatively few system dependencies.

The Cygwin DLL is accompanied by a package of GNU command line utility programs. They're widely used by "makefiles" which co-ordinate software builds, so are invaluable to those wanting to port a build process from a UNIX to a Windows host. In particular, quite a few of them are used by the SDE makefiles.

The Windows release of SDE v5.03 requires the user to install Cygwin first, then install SDE tools using Cygwin facilities. This may change in a future release.

Customers with an active support or maintenance contract with MIPS Technologies can receive support for those Cygwin utilities which are used in our makefiles; any problem with those should be reported and we'll fix them. The Cygwin GNU utilities *not* used in our makefiles are "contributed software" and we don't guarantee to tackle bugs in them.

#### 2.1.1. File pathnames in Windows with Cygwin

UNIX and the world-wide Web use forward slashes "/" to separate the components of pathnames; when MS–DOS introduced pathnames they used back-slashes "/"<sup>5</sup>, and Windows has kept to that. Moreover, full MS–DOS pathnames start with a drive letter such as "C:".

When you use SDE on Windows (courtesy of Cygwin) either pathname format can be used. That doesn't make them equally usable in all cases. For general file system purposes you'll probably tend to use Windows navigation tools, but Cygwin's UNIX-derived applications make large-scale use of backslash as an escape character and you'll struggle to sneak backslashes past UNIX-style command and option parsers. Similar problems are caused by spaces in filenames, and the MS–DOS "x:" syntax can cause confusion in UNIX search paths, which use ':' as a pathname separator (where MS–DOS uses ';').

If SDE users hit problems, it will probably be in *makefiles*. Let us know what happens and we'll try to fix it. The exact relationship between Windows and Cygwin pathnames depends on settings in the Windows "Registry", but in

environments to GNU and other freely redistributable software.

<sup>4</sup> "POSIX" is a set of standards to allow software portability across a very large range of computer systems, which grew up in the UNIX world.

<sup>5</sup> It probably wasn't *just* perversity; MS–DOS applications had already fixed on "/" to mark command line options.

MIPS<sup>®</sup> SDE 5.03 Programmers' Guide

<sup>&</sup>lt;sup>3</sup> Many thanks are due to Cygnus Solutions (now part of Red Hat,

http://www.redhat.com), whose staff carried out this work and opened up Win32

most cases all the following are equivalent:

c:\Windows\System

c:/Windows/System

//c/Windows/System

/cygdrive/c/Windows/System

The further down that list you go, the more compatible you'll be with UNIX-style command and option parsers. Definitely don't expect to get away with spaces, dollar signs, or parentheses in filenames inside a makefile.

Cygwin uses a mapping table called the *mount table*, stored in the Windows registry, to make Windows drive names appear as a single, unified POSIX file system. The mount table concept will be familiar to many UNIX users, but old DOS hands may also recognise it as similar to the nnjoin command, which made individual drives appear to be part of a single file tree. The mount table is manipulated by Cygwin's mount and umount commands. The cygpath command can convert between POSIX and Windows file name formats, in case you need to do that in a "shell script", batch file or *makefile*.

Remote network shares can be accessed directly using the "UNC" //servername/sharename convention – they don't have to be *mounted* first.

A more detailed description of how Cygwin file naming and the mount table works can be found at http://cygwin.com/cygwin-ug-net/using.html.

#### 2.1.2. Text and binary files in Cygwin

Another major schism between the Windows and UNIX world is the convention on how to mark the end of a line in a text file: UNIX programs use a single line-feed character (ASCII LF), while Windows uses a carriage-return, line-feed pair (ASCII CR/LF) and an ASCII SUB (Control-Z) to indicate end-of-file. Therefore on Windows a C program must indicate whether it is writing to a file in text or binary mode, which tells the i/o libraries whether to expand '\n' to CR/LF when writing a file – and vice versa when reading. This is true of Cygwin programs too, but with Cygwin you can control whether this translation occurs on a "per mount-point" basis using the mount command's  $-\mathbf{b}$  (binary) or  $-\mathbf{t}$  (text) option: in a binary mode file system text and binary files are treated identically, i.e. no translation is done and UNIX-style single LF line endings will be written to output files, and expected on input files; in text mode file systems the text conversion indication is honoured.

The choice of which file system mode to use probably depends on the editor you are going to use with your source files. If you use a Cygwin-based text editor (e.g. XEmacs, Emacs, vi, nano, ed), then you'll do best with binary mode. If you already use a Windows program editor which can't be instructed to use UNIX line endings, then you'll do better selecting text mode. In desperation the Windows *WordPad* editor understands UNIX line endings, and may be acceptable for occasional usage – it can be called up from the command line using the write command, for example:

```

$ cd .../sde/examples/hello

$ write hello.c

```

If you need to convert text files between UNIX and DOS line endings, you can use the unix2dos and dos2unix utilities, supplied as part of the optional *cygutils* package<sup>6</sup>. For example, SDE source and headers are supplied in UNIX format, so the following command line run in a Cygwin shell window would convert all of SDE's text files from UNIX to DOS line endings:

```

$ cd .../sde/

$ find kit include examples -type f \! -name "*.lib" | xargs unix2dos

```

<sup>6</sup> Use the Cygwin Setup program to install the *cygutils* package – it's in the "Utils" category.

MIPS<sup>®</sup> SDE 5.03 Programmers' Guide

## 2.2. Environment variables

Environment variables are used in both UNIX and Windows; the best-known is the PATH variable, which specifies a list of directories to search for programs.

Each variable is just a name and associated string value. Whenever one program launches another, all these names and values are copied to the "child" program. By means of that inheritance, the variables are useful for defining global "facts" about the way you use the system which different programs can use to fit in with it; in particular the "*sde-make*" program which orchestrates software builds under SDE uses environment variables to define build rules.

Variables are most usually initialised by running a script which uses one of several flavours of "set variable" command. In UNIX systems the variables are typically set up by your login or your personal command-line shell startup script, so your environment settings depend on your log-in identity. For this purpose Cygwin creates a UNIX-compatible user id and home directory on Windows NT and above – by default that will be "/home/username".

When you install the software on Linux or Windows you'll get a choice between making the software available to all users<sup>7</sup>, and making it available just for you. On Sun and HP, it's probably just for you.

<sup>&</sup>lt;sup>7</sup> It relies on the convention that all users' shell interpreters execute the scripts in directory /etc/profile.d/ when they start up. Both Cygwin and many modern Linux distributions will do that, but on Linux you will need to have "super-user" privileges to be able to create files in that directory.

Chapter 3.

## Installation

Whatever else you skip, please read this section...

## 3.1. Minimum System Requirements

- *Platform*: Any of the following hosts, running one of these named operating systems (of **at least** the specified version number):

- Microsoft Windows NT, 2000, XP on any suitable x86 platform, with Cygwin 1.5.3 or above.

- RedHat Linux 7.1 and above for x86 but pretty much any x86 Linux with glibc version 2.2.3 or higher should be OK.

- SPARC Solaris 2.6 or higher.

- Hewlett-Packard HP9000 HP-UX 10.20 or higher.

If you've got some flavour of UNIX or Windows which isn't on this list and can't be supported by any of the above, please ask or we won't know we're missing you.

- *Memory*: 64Mbytes should be fine for most purposes, but nowadays you'll probably have much more.

- *Disk Space* : 500 Mbytes available.

## 3.2. Environment Variable Setup

The SDE installation process gives the choice to modify the PATH environment variable (making SDE tools directly usable to you) by arranging to run the appropriate *sdeenv* script<sup>8</sup> whenever you start a shell. It uses two approaches, depending on your install-time choice:

- *For all users* : installs copieds of the *sdeenv* files in the /etc/profile.d/ directory, where they will be executed automatically for every user.

- Just for you: adds a line to the end of your personal shell startup script (.profile, .cshrc, or .tcshrc) whic invokes the appropriate *sdeenv* file.

With SDE v5.03 and above, running the tools from a DOS box or Windows "Run" dialog is possible, but is deprecated – you'd have to find your own way of setting the PATH variable and other Cygwin environment variables.

## 3.3. Installation

You should download SDE from the internet: you'll generally find the most recent recommended version at <a href="http://www.mips.com">http://www.mips.com</a>, and follow links to "Products" and "Software Tools"

Installation is "semi-automatic", using shell scripts. It usually works first time, but you should read these notes through before you start and take a little bit more trouble than you might with other software; SDE has hundreds of users, not tens of thousands, and now and again one of you will come up against some configuration problem that we never heard of before.

When you're downloading from internet you'll first obtain the SDE *lite* subset. If you purchased the MIPS<sup>®</sup> Software Toolkit you'll then receive additional components which extend this to form the full MTK version (you can download these using a login name and password we'll send you, or we can email them to you).

<sup>&</sup>lt;sup>8</sup> It can be .../bin/sdeenv.sh or .../bin/sdeenv.csh, depending on your choice of shell.

#### What's in the internet download?

The toolchain is provided as a gzip-compressed  $tar^9$  archive, sometimes called a "tarball" for short. There is a single tar file for each supported host type, with a name like PN00115-xx.yy-2B-MIPSSW-?SDE-va.b.c.tgz. This contains the GNU tools and documentation, plus MIPS Technologies' proprietary examples, libraries, header files, and run-time system. The "?" in the archive file name represents the host type, and the "xx.yy" and "a.b.c" strings are numeric sequences which encode the release number in a reasonably obvious way.

In addition to the per-host tar archive you'll also find some files which are for your information only:

- *README.TXT*: a plain text file, where we document any late updates to the release. It's the final authority about how to go about downloading, and might tell you of errors in or changes to this chapter, so read it.

- *NEWS* : a text file containing the recent release history.

- *sde-guide.pdf*:

- *MD00310-2B-SDE-SUM-xx.yy.pdf*: two different names for the latest version of this manual.

- *PN00119-xx.yy-2B-MIPSSW-SDE-SRC-va.b.c.tbz*: optional source code for the GNU programs, as a *bzip2*-compressed tarball only serious hackers need this.

These files are actually collected up and packaged for delivery inside another "meta" tarball, with a name like IPDP00298-xx.yy-1D-MIPSSW-SDE-HOST-va.b.c-LITE.tgz.

#### Where should you install your package?

In this manual we'll often refer to file pathnames. It would fatten the manual horribly to write them all twice (in Windows and UNIX format); so we'll most often just write them with forward slashes, as used on UNIX, in the Cygwin shell or the makefiles. When you're using native Windows tools, replace each "/" with a "\" and prepend the root of the Cygwin POSIX tree (e.g.  $c:\cygwin$ ).

SDE has a default location: /usr/local/sde5, but this location is not compulsory (if disk space or your system manager dictates). Wherever you choose to install SDE we'll call this the "*SDE root*", and all the files which make up the release will live in subdirectories below this point. In the remainder of this manual we'll write a pathname relative to the SDE root by starting it off with three dots (an ellipsis) like this: .../

**Warning:** DO NOT install SDE in the Windows "\Program Files" directory – or anywhere else where there will be spaces in the pathname. Spaces in the pathname will be seen as separators on every command line or makefile line; it could be worked around, but all the standard makefiles will stop working.

The next sections tell you how to install the package on UNIX or Windows, from the internet - skip the sections you don't need. Do us and yourself a favour; read through to the end of this list before you start, so you get advance warning when we ask you to do something impossible.

Once you've completed the installation you can proceed to Chapter 4 "Quick Start" to try it out.

## Install MIPSsim<sup>TM</sup> simulator and probes

If you purchased the MIPS<sup>®</sup> Software Toolkit, then you will have received a copy of the MIPSsim simulator. You may also have purchased a hardware EJTAG probe. In both cases we recommend that you install these tools first – before installing SDE – following the instructions supplied with these products. This will allow the SDE installation scripts to automatically configure the tools to use your simulator and/or probe.

If you install these tools later – don't worry – you'll just have to teach SDE about them manually. Details about installing and using the MIPSsim simulator and EJTAG probes are in Section 13.1 "MDI Debugging".

<sup>&</sup>lt;sup>9</sup> The *tar* format is familiar to UNIX users, but many Windows packages (including freeware or shareware) can read it. Its virtue is its simplicity.

#### **Remove old SDE**

Don't try to install a new major SDE release on top of an old one. Reorganisations between major releases of SDE are usually substantial enough that it is not possible to merge releases in this way. You must install SDE into a different directory. It is usually safe to install minor revision updates and patches on top of the same major release.

Consult Appendix C "Release History" for details of significant changes since the last release.

#### Windows: Uninstall old SDE and/or Cygwin

Recent versions of Cygwin have a structure which has changed so much that it is not usually safe to install them side-by-side with older Cygwin releases such as B18, B19, B20, B20.1 or 1.0. You should be better off with a new installation in any case. SDE v4.1 and earlier were built on Cygwin B20.1 or B19, so if you're upgrading from one of those releases you'll first have to uninstall your old copy.

To delete SDE v4.0 and above, choose *Remove Algorithmics Free GNU Toolkit* from the *Free GNU Toolkit* folder in your Windows *Programs* menu.

You may need to manually delete or rename any shortcuts to the old release from your Windows desktop.

#### **UNIX/Linux: Uninstall old SDE**

When removing an old SDE installation from a UNIX host you may need to identify and remove any SDE related changes to your .cshrc, .tcshrc, .login or .profile startup files and remove them. For releases prior to SDE v4.0 this means removing definitions of environment variables like GCC\_EXEC\_PATH and LIBRARY\_PATH, which are no longer required, and would confuse the new tools.

#### Windows: Install Cygwin

Go to http://www.cygwin.com and follow the *Install Now!* link. Even If you've already got a recent net release of Cygwin installed, you must still follow these instructions to download the latest updates, and make sure that you are running Cygwin 1.5.3 or above.

When you run the downloaded Cygwin Setup program, one of the first dialog boxes is called "Select Root Install Directory", and it asks you three somewhat confusing questions:

- *Root Directory*: This Windows drive and directory is where the whole of the Cygwin pseudo-POSIX file system will be rooted. If you've had an old version of Cygwin (prior to version 1), such as the one included with SDE 4.x, then this will probably indicate the root of a Windows drive, e.g. "C:\". This is no longer recommended practice for Cygwin instead you should install it in its own sub-directory, to avoid muddling its files up with other Windows programs. We recommend that you edit this field to read "c:\cygwin", or similar.

- Install For: All Users / Just Me: The Cygwin package uses the Windows registry to store its mount table, which it uses to map Windows drives and network shares into Cygwin's unified POSIX file hierarchy. See Section 2.1.1 "File pathnames in Windows with Cygwin" for more details. If you select "All Users" then the Setup program will initialise the "system wide" mount table, shared by all users on this system; desktop and start menu shortcuts will also be created for all users. The "Just Me" option creates the mount table and desktop shortcuts only for the current user.

- *Default Text File Type: DOS / UNIX*: Selects the type of line endings in text files read or written by Cygwin programs. Cygwin defaults to "UNIX" mode, as this creates less problems for programs ported from UNIX, and it's faster but it may not be the right choice for you if you are going to use Windows native text/program editors, in which case you should select "DOS" mode. See Section 2.1.2 "Text and binary files in Cygwin" for more discussion of this issue.

If you're new to Cygwin, the next most confusing choice you'll encounter will be what packages to install. The first time the Setup program is used it will select all packages in the "Base" category, and this is a sufficient minimum to run SDE. But there's lots more interesting software. You might want to add the cygutils package, part of the "Utils" category, which contains the text file conversion tools mentioned in Section 2.1.2 "Text and binary files in Cygwin".

The Setup program can be run again at any time to check for updates to your currently installed packages, or to download and install new contributed packages.

To choose packages from the "Select Packages" list:

- 1) First make sure that the "Curr" button is selected, not "Prev" or "Exp". The "Exp" button selects experimental (beta) releases, which are not recommended for production use.

- 2) You can use the "View" button to cycle between three views of the package list:

- *Category*: a list of packages grouped by category, which sometimes make it easier to browse the list and find useful packages.

- All: a complete list of all available packages, in alphabetical order.

- *Partial*: a list of all packages currently selected for downloading and installation when running Setup after the initial installation this will list available updates to your currently installed packages, if any.

- 3) In both the "Partial" and "All" views, each package shows the currently installed version (if any), and then an embedded "spinner" button. This button selects the action that will be performed to this package when you finally hit the "Next>" button. The possible states are:

- *Skip* : this package is not currently installed don't try to install it.

- *Keep* : this package is installed, but keep the current version don't update it.

- Uninstall : remove this package.

- *Reinstall*: download and reinstall the same version of this package as is already installed.

- *version-number*: A newer, possibly experimental (beta) version of this package exists. Don't select this option, unless you are doing an update run and Setup inserts this for you automatically in the "Partial" view, because it is a "current" update.

Once your Cygwin installation has finished, open a Cygwin "shell window" by activating your new Cygwin desktop icon, or start menu item.

If the shell prompt looks something like this:

Administrator@PCNAME \$

or if the id command says that your name is "Administrator", then you need to update Cygwin's /etc/passwd and /etc/group files, as follows:

```

$ mkpasswd -1 -d | sort -u >/etc/passwd

$ mkgroup -1 -d | sort -u >/etc/group

```

Then close your Cygwin window and open a new one. You should now see your Windows login name as part of your prompt.

Now that you have Cygwin up and running, work inside a Cygwin shell window to install SDE *lite* or SDE: the instructions are the same as for UNIX.

#### **Install SDE**

- 1) You can either download SDE *lite* from http://www.mips.com, and follow links to "Products" and "Software Tools" or you may receive a copy on a CDROM. In either case you will either receive or download one or more compressed *tar* files, with names starting "IPD".

- 2) On Windows: open a Cygwin shell window.

- 3) The file(s) which you downloaded must first be unpacked using the *tar* command. For example:

- \$ cd /tmp

- \$ gzip -dc IPDP00298-01.00-1D-MIPSSW-SDE-LIN-v5.03.06-LITE.tgz | tar xf -

On Windows platforms you can also unpack these files using a program like WinZip or UltimateZip.

In either case, this will leave you with one or more new tar files, named as follows:

| Component                                  | Purpose                          |

|--------------------------------------------|----------------------------------|

| PN00114-xx.yy-2B-MIPSSW-SSDE-va.b.c.tgz    | Sparc Solaris host toolchain     |

| PN00115-xx.yy-2B-MIPSSW-LSDE-va.b.c.tgz    | x86 Linux host toolchain         |

| PN00116-xx.yy-2B-MIPSSW-MSDE-va.b.c.tgz    | Microsoft Windows host toolchain |

| PN00117-xx.yy-2B-MIPSSW-HSDE-va.b.c.tgz    | HP-UX host toolchain             |

| PN00118-xx.yy-1C-MIPSSW-MTK-SDE-va.b.c.tgz | Extra MTK sources                |

| PN00119-xx.yy-2B-MIPSSW-SDE-SRC-va.b.c.tbz | Optional GNU source code         |

Table 3-1: Installable tar files

4) Unpack the appropriate host toolchain tar file into your chosen SDE root directory, for example:

```

$ mkdir ~/sde-5.03

$ cd ~/sde-5.03

$ gzip -dc /tmp/PN00115-5.36-2B-MIPSSW-LSDE-v5.03.06.tgz | tar xf -

```

The '~' in the example is expanded by the shell to the name of your home directory. On Windows you **must** use Cygwin's *tar* command to unpack these tarballs – do **not** use *WinZip*, or any other native Windows program.

- 5) Run the setup script from the newly installed package, e.g.:

- $\$  sh ./bin/sdesetup.sh

This will auto-generate the startup scripts which add the SDE tools to your search path. It will also ask you if you wish to configure one or more "MDI fragments" – configuration files which tell the *sde-gdb* debugger how to connect to a MIPSsim simulator or EJTAG probe; you'll need to enter:

- a) A short name to identify this MDI device, e.g. "mipssim3", "fs2', etc. Use the name "default" if you've only got one MDI device, or for the device which you expect to use most often.

- b) A longer, more descriptive title for this device, e.g. "MIPSsim version 3.4.15" (don't enter the quote marks).

- c) In the case of the MIPSsim software, the name of the directory or folder where you installed it (the same as the MIPSARCHROOT setting in the MIPSsim Guide) if you have more than one version of the MIPSsim software installed then you can set up a separate fragment for each one, each with a unique name;

- d) In the case of a Windows-based EJTAG probe, the name of the probe's MDI DLL e.g. for the FS2 ISA-MIPS probe it is "fs2mips.dll".

If you install MIPSsim software or EJTAG probe drivers later, then you'll have to perform this step manually, as described in Section 13.1 "MDI Debugging".

6) If you purchased the MIPS<sup>®</sup> Software Toolkit then you should now unpack the additional PN00118-xx.yy-1C-MIPSSW-MTK-SDE-va.b.c.tgz archive which you received from us into the same SDE root directory. It contains the extra components which upgrade SDE *lite* to the supported MTK version of SDE. For example:

```

$ gzip -dc /tmp/PN00118-5.36-1C-MIPSSW-MTK-SDE-v5.03.06.tgz | tar xf -

```

7) To ensure that your new tools are immediately available to you, either close your shell window and reopen it, or run the commands displayed at the end of the sdesetup script, e.g.

| <pre>\$/bin/sdeenv.sh</pre> | on bash, ksh, etc |

|-----------------------------|-------------------|

|-----------------------------|-------------------|

| <pre>% source ./bin/sdeenv.csh on</pre> | csh | and | tcsh |  |

|-----------------------------------------|-----|-----|------|--|

|-----------------------------------------|-----|-----|------|--|

Now proceed to the next chapter to try out SDE on a simple example.

Copyright © 1995-2004 MIPS Technologies, Inc. All rights reserved.

## 3.4. Multi-User Installation

If you want to install a single copy of the SDE toolchain to be shared by a group of programmers, simply follow the instructions above, but install the release into a well-known, shared directory, e.g. /usr/local/sde5 or /opt/sde5.

You will then need to give each user their own copies of the .../sde/kit and .../sde/examples directories, so that they can build libraries and programs without interfering with each other. As long as the two directories remain at the same level (e.g. ~jones/sde5/kit and ~jones/sde5/examples) then the example makefiles will work correctly.

Chapter 4.

## **Quick Start**

If you are impatient to try out SDE, or want to confirm that your software installed OK, then follow these instructions to build and run one of the example programs using the GNU MIPS simulator (sde-run). If you have problems at any stage, support can be on hand; see Chapter 24 "Getting Support" for contact information.

In this example we're going to use the **GSIM32L** target, which implies: a GNU simulator "target"; MIPS32<sup>™</sup> code; little-endian.

- 1) If you are running on Windows, then open a Cygwin shell window.

- 2) Change directory to the "hello world" example program:

```

$ cd .../sde/examples/hello

```

We're not going to show you native Windows pathnames, though you can use them (with some caveats): see the notes on pathnames in Section 2.1.1 "File pathnames in Windows with Cygwin".

- 3) Build the example (the upper/lower case distinction IS important):

- \$ sde-make SBD=GSIM32L

- 4) Run the program using the GNU simulator:

```

$ sde-run helloram

```

5) You can also run the program using the GNU debugger in command-line mode (same simulator):

```

$ sde-gdb -nw helloram

(gdb) target sim

(gdb) load

(gdb) run

...

(gdb) quit

```

- 6) Try running the program using the *Insight* graphical interface to *gdb*:

- i) Start *gdb* with the command "**sde-gdb helloram**" (i.e. omitting the "**-nw**" argument).

- ii) The main Insight *Source Window* should open. If the *Console Window* doesn't also appear, then click on the "console" icon in the source window's toolbar. This allows you to see output messages from the program being debugged.

- iii) Click the "Run" icon (the running man) in the source window toolbar the *Target Connection* dialog box will appear. Select "GNU Simulator" in the *Target* field of the dialog box, and click "OK".

- iv) The program will be "downloaded" to the simulator, then run until it hits a breakpoint in main().

- v) Click the "Continue" button  $(\rightarrow \{\})$  on the toolbar. The program will print "Hello World!" in the console window, and then stop at the next breakpoint, in the C library exit() function.

- vi) Select "Exit" from the source window's "File" menu.

See Chapter 12 "Insight Graphical Debugger" for more details. If you now want to try porting your own program to run on the GNU simulator, then see Chapter 9 "Porting an ANSI C Program", which provides guidelines on porting ANSI/POSIX C programs with SDE. If you want to try running example programs on real hardware, or on a more accurate software model such as the MIPSsim simulator, then see Chapter 7 "Target Specific Libraries" and/or Section 13.1.1 "MDI Debugging with the MIPSsim<sup>™</sup> Simulator".

Don't forget that detailed manuals can be viewed with your web browser, see Chapter 6 "Online Documentation".

Chapter 5.

## **Overview**

This section provides a quick overview of the major components of SDE, particularly aimed at those for whom a command-line interface is not obviously a good idea.

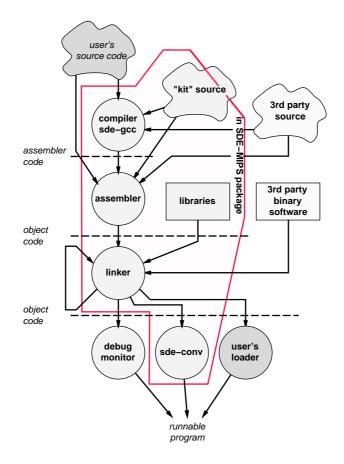

Figure 5-1 Programs, libraries and source files in SDE

#### In Figure 5-1:

- The round objects are programs you run. You don't often need to know of the programs which really compile, assemble and link: they are generally orchestrated by the single "driver" program *sde*-*gcc*.

- The dark grey objects show the user-supplied files; intermediate grey are in SDE, and the light ones might be third-party software, if you use it.

#### Command lines, make and makefiles

An "integrated development environment" (IDE) like Microsoft's *Visual*  $C^{TM}$  has become the standard development tool in the PC world. IDEs tie the basic compilation tools and libraries into a complex web of debuggers, editors, and other software.

By contrast, UNIX® command line tools were designed to be glued together using simple text files – shell scripts and "makefiles" (we'll say something about those just below). It's much simpler for us to supply and maintain individual tools which build on the wonderful free software that's out there.

## **Program Editor**

Since we're not supplying an integrated environment, you need to bring your own program editor. There are lots of fairly good ones about; it's worth rooting around on the web, since you probably spend a lot of your life editing and the obvious tools available on every PC are pretty basic. The author (and all of the SDE team) use and warmly recommend XEmacs or Emacs, which takes a while to learn but is magical. It's free from

http://www.xemacs.org and runs on everything. But we understand that this is not so much an editor, more a way of life; editors are a matter of personal preference.

Your editor should allow you to fire off "makes" without quitting the editor, catch any compiler errors and interpret them to automatically locate you in the file where the error was detected. Many decent editors can understand GNU C's error formats well enough to do this; though you might have to teach them.

### Make

Once you've got your editor, the job of SDE (whether IDE or command-line based) is to take a bunch of source files, libraries and the like which are to make up one or more useful program(s), and to run appropriate compilation, assembly and link operations until you get a runnable program.

This is always complicated, but when you're (for example) building applications "native" much of the complication is hidden by the OS' defaults – most of the time, everything can be done the standard way. The less of an operating system you have, though, the more complication shows through.

In SDE the build job is directed by the *sde-make* program which finds out what to do to build a particular set of files from a plain text file which you've prepared – the *Makefile*. All the examples in SDE come with alarmingly elegant "Makefiles" ready to run.

For all the grisly detail see the GNU manual [Make], but here's a comforting four-paragraph guide:

In simple cases, where the source and target files all live in one directory, *make* will by default take its instructions from a file called Makefile.

Inside the makefile, you'll find entries which look a bit like this:

```

target: depend1 depend2 ...

do-this

do-that

```

(That's a tab character at the beginning of the action lines, not just spaces).

When asked to "make target", this will check to see whether the file target (if it is a file) is older (earlier write time) than any of the files depend1 etc. If one of those files has been changed, it will run the commands *do-this*, *do-that* in sequence, just as if those command lines had been typed at the shell prompt.

If you don't specify a target for *make*, the default is the first target in the makefile; it's conventional to lay out the file so you can build the most obvious target in your "project" by just typing *make*.

Of course, over the years *make* has grown lots of other facilities, all of which seemed to be a good idea at the time, so a modern makefile is fairly scary – as is the GNU manual [Make]. Some important extra features include:

- *Wildcards in targets* : targets can be specified with wildcard names, like \* . c, specifying the default action for files which look like that (you can override these with a specific entry).

- *Variables*: the ugly syntax "\$(CFLAGS)" substitutes the (string) value of a variable CFLAGS, which may be set earlier in the makefile or inherited as an *environment variable*.

- *Included sub-makefiles*: lines starting include ... have the effect of calling in another makefile just like a C #include, the lines of the file are treated just as if they were part of the original makefile. SDE uses the facility extensively, using nested makefiles to share information up and down its file hierarchy.

The golden rule of "make": *NEVER* write your own makefile (at least, not until you're experienced enough to understand why we said that). Instead, copy something vaguely like what you're trying to do and hack it into shape. That way, the bits you don't understand will just quietly carry across.

Oh, and don't put spaces or other non-alphanumeric characters in your file names; make will hate it.

## **C** Compiler

This is our version of the Free Software Foundation's ANSI-compatible GNU C Compiler (called *sde-gcc*<sup>10</sup>). This version incorporates superb optimisation for RISC processors, such as MIPS architecture processors. It also includes many of our own bug fixes, enhancements and optimisations.

In practice, the compiler, C++ compiler, assembler and linker are all usually invoked as *sde*-*gcc*, which (by default) figures out what to do with a file based on the filename extension.

## C++ Compiler

We also provide the GNU C++ compiler (sde-g++). It is a true compiler (not a converter or translator) which conforms to the 2nd edition of the C++ language definition.

The sde-g++ compiler supports modern C++ features, and benefits from all of the enhancements and optimisations in the C compiler. However use of C++ exceptions and/or run-time type identification incur a significant size overhead. If these features are not required by your code, then they can be switched off individually using the **-fno-exceptions** and **-fno-rtti** options, respectively.

The **-fembedded**-**cxx** option enforces compliance with the "standard" Embedded C++ subset, which also prohibits exceptions and RTTI, together with *mutable*, namespaces, templates, and complex run-time casting.

## MIPS<sup>®</sup> Assembler

SDE's version of the GNU assembler ( $sde-as^{11}$ ) is, as far as is possible, source code compatible with the "standard" MIPS assembler syntax, including the modern MIPS32<sup>TM</sup> and MIPS64<sup>TM</sup> instruction sets and their "Release 2" variants, together with the historical MIPS I<sup>TM</sup> through MIPS V<sup>TM</sup> ISAs, and standard extensions like the MIPS16<sup>TM</sup>, MIPS16e<sup>TM</sup>, SmartMIPS<sup>TM</sup>, MIPS-3D<sup>TM</sup> and MDMX<sup>TM</sup> Application Specific Extensions (ASEs).

## **Binary Utilities**

The GNU binary utilities support a version of the ELF object code format. Our ELF is pretty compatible with other MIPS tools; ELF is probably the most widely used family of object codes for 32-bit CPUs<sup>12</sup>. The tools are described in detail in the GNU manual [Binutils] and include:

- *sde-ld*: the link editor/locater (usually automatically run by *sde-gcc*), which supports sophisticated script files for building complex images read [Ld]. Such features are never without cost; if your system can use simple program images, your project will be blessed.

- *sde-size* : prints the size of the various sections in an object file.

- *sde-nm*: prints the names held in an object file's symbol table, sorted by address or by name.

- *sde-strip* : removes an object file's symbol table, to save on disk space.

- *sde-ar*: an object code archiver/librarian.

- *sde-objdump* : prints out parts of object files for inspection, including disassembly of code sections.

- *sde-strings* : displays any readable ASCII text strings in an object file.

- *sde-objcopy*: copies object files, optionally converting object formats, and including or excluding named sections.

- *sde-gprof*: profiling report generator, with its own manual [Gprof].

- *sde-readelf*: reports the low-level structure of an object file (use *sde-objdump* to read the contents).

<sup>&</sup>lt;sup>10</sup> All the GNU tools are named like this; it avoids name clashes with other versions of GNU CC which may be installed on your system. Previous versions of SDE also included tools without the *sde* – prefix, but these are no longer provided.

<sup>&</sup>lt;sup>11</sup> It would be more consistent to call it sde-gas; the reasons for not doing so are historical.

<sup>&</sup>lt;sup>12</sup> Don't assume that this means that software written for some other ELF dialect will port easily to the MIPS version. ELF is more a family of standards than a standard.

## **ECOFF** compatibility

Most of the binary utilities such as sde-ld and sde-objcopy offer some support for object files and libraries in the "ECOFF" format produced by the 1980s MIPS Computer Systems native compiler.

## **Download Tools**

To download the executable binary files produced by the linker to an evaluation platform or PROM programmer requires additional conversion and communication tools.

- *sde-conv* : converts a binary object file into a number of formats, including Motorola S-record, MIPS flash download, IDT/sim binary, LSI PMON fast format, and Stag (prom programmer) binary.

- *edown*: a simple communications tool which downloads a file, typically produced by *sde-conv*, to a remote evaluation board using the ETX/ACK flow control protocol.

## Libraries

C is nothing without its libraries; SDE has the standard C library and math library supplied pre-compiled for a range of different MIPS ISA options; the version you need is picked automatically according to the flags you give the compiler – see Section 10.3 "Multilibs". Customers who purchase the MIPS<sup>®</sup> Software Toolkit also receive the full libraru source code – see Section 10.4 "Source Code".

The libraries conform to the appropriate ANSI standard (X3J11), and CPUs with no floating point math hardware can take advantage of our IEEE–754 compliant floating point emulator, provided as a separate library.

## **Header Files**

A complete set of ANSI and POSIX-compatible C and C++ header files is provided. In addition there are machine-specific header files covering a variety of MIPS architecture processors, and associated support chips.

## **Embedded System Kit**